いわゆるCMOSアナログスイッチ等と呼ばれている素子の動作について考えます。サブストレートの接続が独立している、いわゆる4端子MOSFETで、ソースとドレインの区別が無い使いかたなど、いつもと違うので直感がなかなか働きませんんが、まぁ慣れです。

以下はTIのCD4066Bのデータシートにある、内部の構造の解説です。ここで、上に「Switch」とあるMOSFET2個の部分と、反転バッファについては4016と共通です。

問題は残りのMOSFET3個から成る部分で、その動作を考えることが本稿の目的です。

まず前提となる4016の動作について考えます。

さきほどの構造から、4016相当の部分だけを取り出して繋げ直すと、次のようになります。

NチャネルMOSFETの側のサブストレートがVssに接続されるのが明示的になっているのは、4066の図に合わせているからで、PチャネルMOSFETの側のサブストレートも同様にVddに(明示なく)接続されており、単純で対称的な形であることがわかります。

以下、Vddに近い電圧のことを H、Vss に近い電圧のことを L と表現します。

CMOSアナログスイッチは、PチャネルMOSFETではゲートがL、NチャネルMOSFETではゲートがHの時に、それぞれのドレイン-ソース間が導通状態になることをスイッチに利用したもので、入力からつながっている反転バッファの1個目は単なるバッファですが、2個目はPチャネルとNチャネルでLとHが逆なのでそれに合わせるために反転しています。

その導通状態の時、InおよびOutの電圧がLに近い時はPチャネル側はVgsが足りなくなって導通が悪くなり、主にNチャネル側がInOut間の導通を担っていることになります。逆にInOutの電圧がHに近い場合はPチャネル側が導通を担っています。

以上のように、トランジスタの使いかたとしては普段見慣れていないというだけで、基本原理としては単純な部品といえます。

4066の構造を再掲します。

Nチャネル側のサブストレートの電位が、Vss直結ではなく、謎の制御部分が追加されています。これの動作を以下、考えてゆきます。

まず、制御入力がLで、スイッチ全体としてはオフ(非導通)になっている時は、

こんな感じで、上の2個のMOSFETはオフ、下のNチャネルMOSFETはオンになりますから、右にあるNチャネルMOSFETのサブストレートはVssに接続され、4016の場合と同様に働くことになります。

こちらでは逆に、Vssと接続している側のNチャネルMOSFETはオフに、その上の2個のMOSFETはオンになりますから、結局、右にある2つのMOSFETのうちの下のNチャネルMOSFETのサブストレートは、Inの電位(Vis)に近い電位になる、ということになります。

InおよびOutの電位(導通状態ですからだいたい近い電位になる)がLに近い側の時には、これらのNチャネルMOSFETは結局、サブストレートがソースに接続されている3端子のMOSFETの場合と同様の動作状態になっていて、ゲートはHですから安定して導通状態になっているということになります(説明が循環的ですが、そもそもブートストラップっぽい感じの回路になっているのでしょうがないわけです)。

----

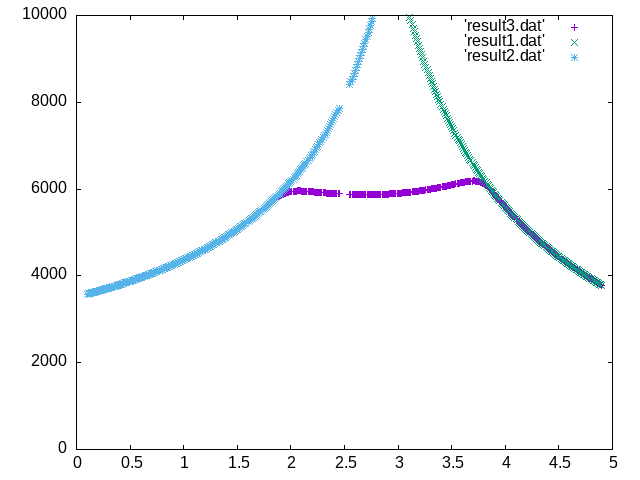

問題はInおよびOutの電位がHに近い側の時で、4016の場合と同様基本的にはPチャネルMOSFET側で導通させるわけですが、一般にPチャネル側は特性が良くありませんから、電位がかなりHに近づくまでの間、Nチャネル側で補助させるのが、結局のところ、この付加回路の目的です。Nチャネル側のMOSFETで、ゲート電位と導通させている信号との電位差がVthよりも少なくなってしまうと、Pチャネル側だけで導通させている、という状態になります。

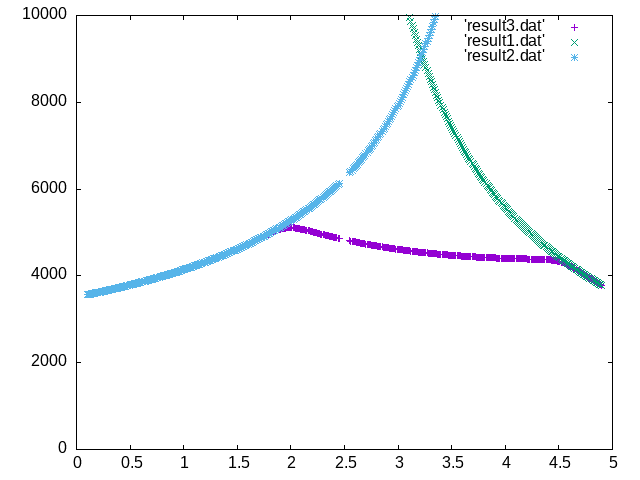

そしてその時に、Inの電位を利用して、Nチャネル側のサブストレートの電位を上昇させることで、RDSの上昇を緩やかにしている……と思われます(私がMOSFETの動作をあまりよくわかってないためですが、シミュレーションの結果を見ると、そのような感じです)。以下にそれぞれの回路のみですが再現して(素子の実パラメータまでではない)シミュレーションした結果を示します(実際の4016乃至4066を再現しているものとして流用されるとまずい、といったこともあり(そのレベルでは全く再現していない)、非公開としたいと思います。そのへん注意して扱っていただけるのであれば、個人的にはお渡しできますのでご連絡ください)。

4016の場合

----

4066の場合