NHK『電子立国』(旧)で少し紹介されたこともあり、その名前と概略は知られている4相方式ですが、電子回路としてシミュレーションできるような詳細は近年ではあまり知られていないのではないでしょうか。また、Wikipedia(en)の記事Four-phase logicの動作原理の解説はわかりにくい感じがします。

というわけで、4相論理についてシミュレーションを動かすまでの大体の解説です。

参照文献として『CMOS VLSI設計の原理』を使います。20年以上前の本ですので、現在購入するならもっと新しい本も選択肢に入ると思いますが、基本原理については定本としてほぼ間違いないでしょう。なお、『電子立国』単行本の解説は、あまり読み込まないほうが良いでしょう。たとえば「四種類のパターンを用意したのは、おそらく入力、演算、記憶、表示の四つの機能を想定したうえでのことに違いない」等、かなり見当違いの記述も少しあり、混乱すると思います。もしシャープの電卓に関して気になるならば『電卓技術教科書 研究編』をおすすめします。大きい図書館に意外とあります。

まず「4相レシオレス」の「レシオレス」からやっつけます。「レシオレス」(ratioless)は「レシオ化されている」(ratioed)の逆で、IC中のトランジスタの面積( = 駆動力)に意図的な比を付けず、均等なパターンで設計するもので、集積度の点でも有利です。

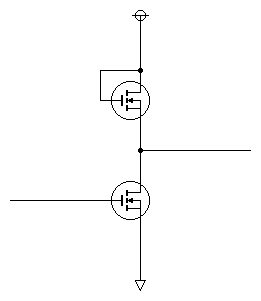

レシオ化されている設計の論理NOTゲートは、以下のような回路になります。

ディスクリート(単品部品)のMOS FETとIC中では、実は重要な違いがあるのですが、それについては後で触れます。ここでは原理の説明としてディスクリートの記号を使います。

ここで、下側のトランジスタのゲート端子が入力で、それにより下側のトランジスタをオフ/オンすることで、右に出ている出力の電圧をハイ/ローに振ります。上側のトランジスタは常にオンで、いわゆる負荷として働いています。

下側のトランジスタがオフの時は、出力に「電源電圧 - 上側トランジスタのスレッショルド電圧」の電圧があらわれます。この電圧をハイとみなします。MOS FETのスレッショルド電圧はディスクリート部品ではバラつきがありますので、3V程度まで余裕を見た場合は電源電圧を10V程度に設定する必要があります。(ゲート電圧にゲタを履かせる、代わりに単なる抵抗を使う、PチャネルのFETを使ってレベルシフトを防ぐ、等、他にもいくつか手法は考えられますが、ここでは流します)

下側トランジスタがオンの時は、上下のトランジスタ共に電流を流しますから、出力にあらわれる電圧は上下のトランジスタで分圧したものになります。この時、出力電圧をローとして十分に下げるには、上側トランジスタを下側トランジスタに比べて、十分に駆動力が小さいものにする必要があります。同時にFETの半導体的な動作領域としては、上側トランジスタはドレイン電流がVgsによって抑えられている定電流特性の飽和領域、下側トランジスタはドレイン電流がVdsによって抑えられている線形領域で動作させていることになります(FETの「飽和領域」は、バイポーラトランジスタの「飽和領域」と逆であることに注意)。

以上のように、トランジスタの駆動力に比を持たせることで論理回路を構成する方式を「レシオ化された」(ratioed)と言います。出力の駆動力に影響しますから、小さくしたい(図の上側の)トランジスタをあまり小さくし過ぎることもできませんし、直流的に電流が流れる場合がありますから、せっかくMOS素子を使っているのに、消費電力の点でも不利です。

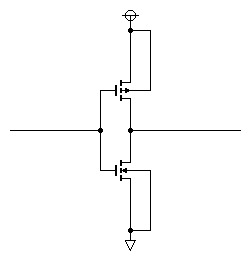

続いて、現在おそらく最も多用されている、静的論理CMOS ICについて説明します。

図は、『CMOS VLSI設計の原理』の図5.1にある回路の一つ(論理NOTゲート)です。

上側はPチャネル、下側はNチャネルのMOS FETです。左側からの入力がローの時、上側のトランジスタがオン・下側のトランジスタがオフになって、右側に出ている出力がハイになります。入力がハイの時は、上側のトランジスタがオフ・下側のトランジスタがオンになって、出力がローになります。

PNそれぞれのスレッショルド電圧にもよりますが、中途半端な入力電圧にしたりしない限り、電源とグラウンドが直流的に接続されることが無いので、消費電力の点で有利です。レシオレス設計で良く、NチャネルとPチャネルの両方のMOS FETをチップ中に作り込むことが容易になってからは多用されるようになりました。

この回路のような、入力の他に同期信号などがない論理回路の方式を「静的論理」と言います。それに対して、本稿でこのあと説明する4相方式などを「動的論理」と言います。

もう一つ、この回路図で注意すべき点として、バルク(MOS FETの右側に3個あるうちの中央の端子)がトランジスタのその場でソース端子に直結されているのではなく、別の配線で電源(ないしグラウンド)に接続されていることが挙げられます。特に筆者のようなラジオ少年上がりで、専門がハードウェアでない人にはあまり慣れのない点です。

IC内部のMOS FETはこのようにするほうが一般的で、このためディスクリートの(3端子の)MOS FETにあるようなソースとドレインの接続上の区別がありません。その結果としてFETの真の姿として、ソースとドレインは対称に働きます。

ですのでMOS FETの動作についても、Nチャネルの場合は「ゲートの電位をバルクからVthより上げると、ソース-ドレイン間が導通する」、Pチャネルの場合は「ゲート電位をバルクから-Vthより下げると、ソース-ドレイン間が導通する」といったように、整理し直しておく必要があります(本稿では全てノーマリーオフのエンハンスメント型FETを前提とします)。

またMOS FETの構造上、バルクとソース及びドレイン間には寄生ダイオードが存在するわけですが(回路図記号中の矢印はこのダイオードを表現している)、この回路図のように接続すれば電位関係上無視して良いわけです。ですので、ICを前提とした説明ではバルクは完全に省略されていることも多いですが、この解説では省略しません。以上のようなIC中のMOS FETに特異な点は、シャープ式(ロックウェル式)4相方式で重要になります。

Wikipedia(en)にもDynamic logic (digital electronics)という記事があるので参考にしてください。

色々な方式が考えられ得ますが、一言でざっとまとめると、クロックのようなデータとは別の信号によりタイミングを合わせて論理演算を行う方式で、初期のコンピュータ(電気試験所のETL Mark-IIIやMark-IVなど)やトランジスタ以外の論理素子(例えばパラメトロン)などでも見られる方式です。

MOS ICでは、ゲート端子が容量性で直流抵抗が高いことを利用し、充電・放電・保持などの相を持ちます(『電子立国』では、間欠的に駆動できるので省電力という点が強調されていましたが、直流的に電流が流れないことがキモで、間欠駆動でも動作することは副次的な効果と見るべきでしょう)。

まず、最も単純な単相方式のNOTゲートから見てみます。

ここで、単相クロックφがローの時をプリチャージサイクル等と呼び、上のトランジスタがオンになり出力がプリチャージされます。φがハイの時を判定サイクル等と呼び、その間は入力の状態が安定である必要があります。判定サイクルで放電が必要な場合は放電され切った時から、次のプリチャージサイクルでチャージが始まるまでの間が、この回路の出力が有意な期間です。

CMOSではなくNMOSのみで構成する方法など、この回路やこの後で説明する回路には様々なバリエーションが考えられますが、ひとつひとつ挙げることはしません(1970年頃にそのようなバリエーションの特許が多数取られています)。

このような論理ゲートを組合せて、一つの単相クロックで回路全てを動かそうとするのは、あきらかに無理があります。"φ" と "notφ" の2相でも苦しいので、そこで各論理ゲートに状態としてプリチャージと判定の他に保持状態を持たせ、多相(4相)のクロックで駆動する方法が考えられます。

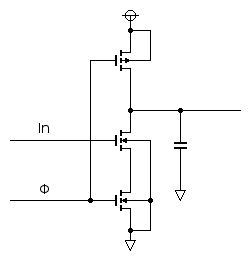

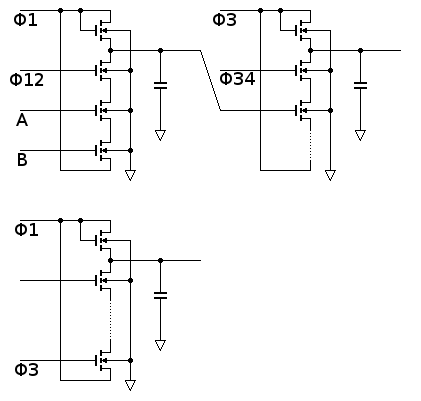

ここではまず最初の1例として、『CMOS VLSI設計の原理』の図5.56、および§5.2.3のタイプBの4相構造回路を(やはり論理NOTゲートを例として)紹介します。

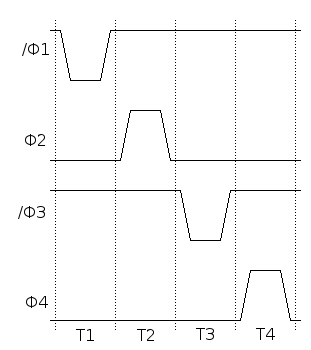

4相のクロックは基本的には次のようになります。

クロックが一周する時間をTとして、その1/4を最初から順番にT1〜T4とします。

T1では一番上のトランジスタがオンになり、出力をプリチャージします。この時一番下のトランジスタもクロック/φ1の信号によりオフになっています(ここではあまり意味がありませんが、次に示す修正で意味を持ちます)。

T2では上から2番目のトランジスタがオンになり判定サイクルになります、この時に入力inに従って論理演算がおこなわれます。

T3・T4ではこの回路(の出力)の状態はそのまま保持され、/φ3とφ4で駆動される次段(ないし前段)の論理回路が働きます。

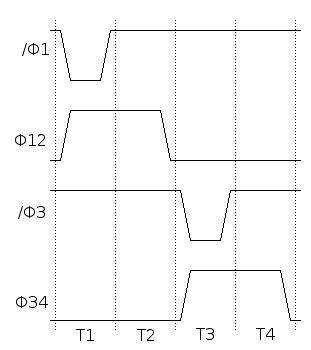

『CMOS VLSI設計の原理』の説明によれば、このままでは電荷共有(https://en.wikipedia.org/wiki/Charge_sharing)の問題があるため、クロックの波形を次のように修正します。

/φ1とφ12がオーバーラップしますので、この修正後の場合は一番下のトランジスタが無いと、直流的に電源とグラウンドが接続される時間が発生してしまいます。

またクロックの波形において、切り替わりの間(縦の点線を入れた場所)にマージンを持たせていますが、安定した動作をさせるためには必要なマージンのようです。ウィキペディアの4相論理の記事や、その元と思われるRob Wilsonさんによる解説では簡略化されていますが、『電子立国』単行本中の図や『電卓技術教科書 研究編』p.177の第2・83図ではマージンが明示されていて、『電卓技術教科書 研究編』p.178には「重なりがあると誤動作を起こすので,破線で示すように一定の間隔を設けています」という記述があります。Wikipedia(en)のトランスピュータの記事中にも、"The internal clock actually had four non-overlapping phases" という記述があります。

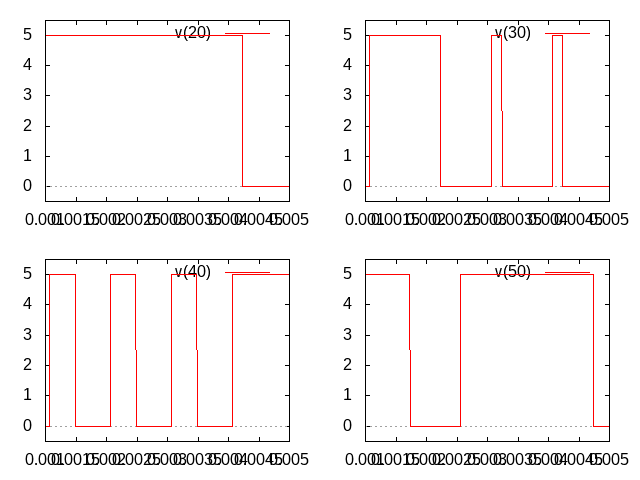

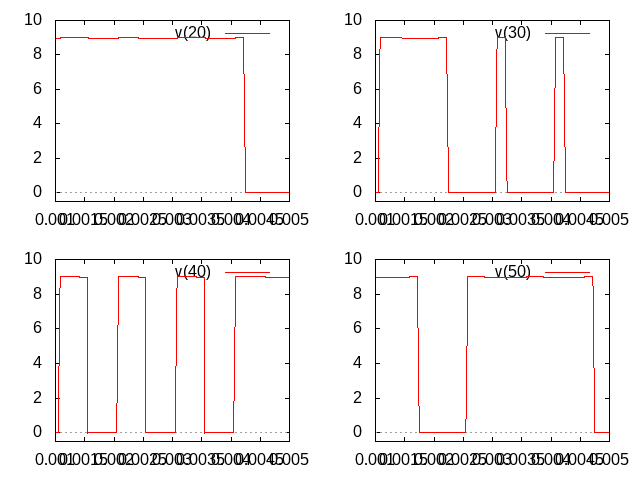

以上の構造の回路で実際に半加算器を構成し、SPICE3の電子回路記述としたものと、そのシミュレーション結果をプロットしたものを示します。

SPICE記述にいくつか補足します。まず、MOS FETは現実的なモデルではなく、最小限のパラメータ以外はデフォルトにしています。一部のノードに1フェムトFのキャパシタを記述してあるのは、この現実的でないMOS FETのためにシミュレーションが不安定になるようでしたので、それの予防のためです。

MOS FETのパラメータで相互コンダクタンス KP=0.1 としてあるのは、デフォルトでは小さすぎる値になって電流が少なすぎるためです。本当はIC上の矩形サイズLとWを反映するような設定とし、LとWを適当な値に設定すべきですが手抜きしました。スレッショルド電圧を VTO=3 と大きめにしたうえで、電源電圧(およびクロックのスウィング)を5Vにしていますので、CMOS構成にしないと正しく論理動作しません。

また、type2とtype4の回路については解説は略します。

筆者は実験していませんが、この回路は(バルク端子の接続は再現できませんが)ディスクリートの部品を使って動作確認ができるものと思います。

『CMOS VLSI設計の原理』で説明されているタイプAの4相論理や、特許資料を調べると数多く出てくるように、他にも構成方式があります。『電卓技術教科書 研究編』p.177にも、「4相方式にもいろいろ考えられていますが,」とあります。

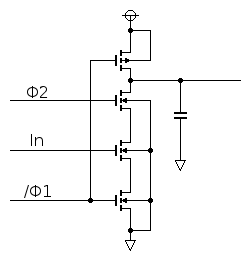

本稿の最終節であるこの節では、『電子立国』や『電卓技術教科書 研究編』で紹介されているロックウェル-シャープ流(実はWikipedia(en)の記事もこれと同じ)の回路方式を説明します。ただし、直感的にわかりやすいNMOS正論理で説明します(『電子立国』や『電卓技術教科書』では負論理。Wikipedia(en)の記述のベースとなっていると思われるRob Wilsonさんによる解説にも "(I'm using NMOS as it's easier to understand, in my humble opinion)" とあります)。負論理PMOSでも、グラウンドを基準(0V)としてクロックを負の側に振り、その負の電位を「アクティブ」と考えれば全く同様に扱えます。

まず、本稿の最初のほうで説明した、ディスクリートの3端子MOS FETとIC内でのバルク端子の接続の違いにより、プリチャージ後の電荷の扱い方が変わるという点を説明します。

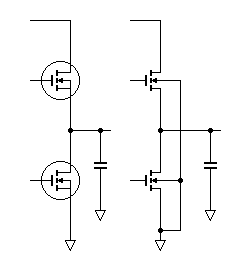

次の回路図の比較を見てください。

ここで、下のトランジスタについてはバルク端子の接続に電気的な違いはありません。しかし上のトランジスタについては、バルク端子が接続されている位置が変わってきます。

左の接続では、電荷をプリチャージした後、電源線(一番上の線)の電位を下げてしまうと、FET内の寄生ダイオード(トランジスタの記号中の矢印)を通してせっかくキャパシタにチャージした電荷が抜けてしまいます。一方、右のような配線であれば電源線の電位を下げてしまっても、ゲート端子の電位を上げない限りは電荷は保持されます。

このことから、電力供給自体を電力線ではなく、クロック線から行うという発想が出てきたのではないかと思います。

さらに、グラウンド側について考えます。

前節の回路で、プリチャージ時に電流が通り抜けないように、一番下にオフになるトランジスタを置いたわけですが、これを電位関係として考えれば、こちらも同じクロック線にしてしまうことができます。プリチャージ時以外は0Vになるわけですが、それは要するにグラウンドと同じとして扱うことができます。

以上のようなわけで、通常は電源とグラウンドになる一番上と一番下の線が、φ1とφ3のクロックになっているわけです。

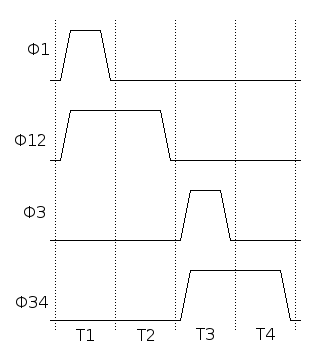

Wikipedia(en)のFour-phase logicの記事にある回路図を、本稿のスタイルに書き換えると、次のようになります。

またクロックは全て正論理で次のようになります。

こちらについても、前と同様に実際に半加算器を構成し、SPICE3の電子回路記述としたものと、そのシミュレーション結果をプロットしたものを示します。

この回路では、スレッショルド電圧による信号レベルのシフトがありますので、スレッショルド電圧は1V、電源電圧(クロックのスウィング)は10Vにしてあります。

4相論理方式について、必要となる背景知識まで踏み込んで、一通り解説しました。4相論理方式自体については、基本的な構成方式の一つと、少々トリッキーなロックウェル-シャープ方式について解説しました。

コメント等ありましたら @ksmakoto か、ksmakoto ◎ dd ● iij4u ● or ● jp 宛に(spam送信先探査避けのため加工しています)メイルでお願いします。